### **NOVOSENSE**

# High Reliability Reinforced Isolated Amplifier with Integrated Isolated Power Supply

Datasheet (EN) 1.0

#### **Product Overview**

The NSI3600D is a high performance isolated amplifier with integrated isolated power supply that accept fully-differential input of ±250mV. The integrated isolated power supply enables single-power operation on the low side of the device without the need for a separate isolated power supply for the high side, effectively reducing the board area. The fully differential input is ideally suited for AC or shunt current monitoring in high voltage applications where isolation is required.

The device has a fixed gain of 8.2 and provides a differential analog output. The low offset and gain drift ensure the accuracy over the entire temperature range. High common-mode transient immunity ensures that the device is able to provide accurate and reliable measurements even in the presence of high-power switching such as in power supply and motor control applications.

The integrated isolated power supply detection and the open-drain diagnosis output simplify system-level design and diagnostics.

# **Key Features**

- Up to 5000V<sub>rms</sub> Insulation voltage

- ±250mV linear Input Voltage Range

- Low Offset Error and Drift:

±0.2mV (Max), ±3μV/°C (Max)

- Low Gain Error and Drift:

±0.3% (Max), ±50ppm/°C (Max)

- Low Nonlinearity and Drift:

±0.05% (Max), ±1ppm/°C (Typ)

- SNR: 84dB (Typ, BW=10kHz), 71dB (Typ, BW=100kHz)

- Wide bandwidth: 350kHz (Typ)

- High CMTI: 150kV/μs (Typ)

- System-Level Diagnostic Features: integrated isolated power supply detection

- Operation Temperature: -40°C ~125°C

- RoHS-Compliant Packages: SOP16(300mil)

# **Safety Regulatory Approvals**

- UL recognition: 5000V<sub>rms</sub> for 1 minute per UL1577

- CQC certification per GB4943.1

- CSA component notice 5A

- DIN EN IEC 60747-17 (VDE 0884-17)

# **Applications**

- · Shunt current monitoring

- Power Supplies

- Charging Piles

- Energy Storage Systems

- Solar Inverters

- Motor Drives

#### **Device Information**

| Part Number   | Package       | Body Size        |

|---------------|---------------|------------------|

| NSI3600D-DSWR | SOP16(300mil) | 10.30mm × 7.50mm |

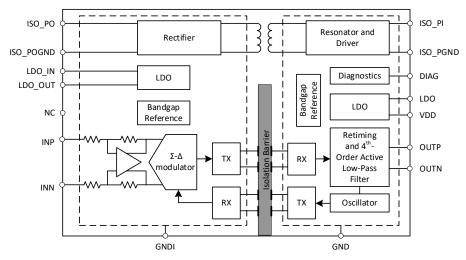

# **Functional Block Diagrams**

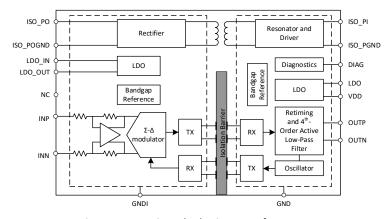

Figure 1. Function Block Diagram of NSI3600D

# **INDEX**

| 1. PIN CONFIGURATION AND FUNCTIONS                                                        | 3  |

|-------------------------------------------------------------------------------------------|----|

| 2. ABSOLUTE MAXIMUM RATINGS                                                               | 4  |

| 3. ESD RATINGS                                                                            | 4  |

| 4. RECOMMENDED OPERATING CONDITIONS                                                       |    |

| 5. THERMAL INFORMATION                                                                    |    |

|                                                                                           | _  |

| 6. SPECIFICATIONS                                                                         | 5  |

| 6.1. ELECTRICAL CHARACTERISTICS                                                           |    |

| 6.2. TIMING DIAGRAMS                                                                      |    |

| 6.3. Typical Performance Characteristics                                                  | 7  |

| 7. HIGH VOLTAGE FEATURE DESCRIPTION                                                       | 11 |

| 7.1. Insulation and Safety Related Specifications                                         | 12 |

| 7.2. Insulation Characteristics                                                           |    |

| 7.3. REGULATORY INFORMATION                                                               | 13 |

| 8. FUNCTION DESCRIPTION                                                                   | 14 |

| 8.1. Overview                                                                             |    |

| 8.2. ANALOG INPUT AND OUTPUT                                                              |    |

| 8.3. ACCURACY RELATED PARAMETERS                                                          |    |

| 8.3.1. Input offset V <sub>OS</sub> and Gain Error E <sub>G</sub>                         |    |

| 8.3.2. Input offset drift TCV <sub>os</sub> and Gain error thermal drift TCE <sub>G</sub> |    |

| 8.3.3. Nonlinearity                                                                       |    |

| 8.3.4. Power-Supply Rejection Ratio                                                       |    |

| 8.3.5. Common-Mode Rejection Ratio                                                        |    |

| 8.3.6. Total Error Calculation                                                            | 16 |

| 8.4. ISOLATED POWER                                                                       |    |

| 8.5. DIAGNOSTIC OUTPUT                                                                    | 18 |

| 9. APPLICATION NOTE                                                                       | 20 |

| 9.1. Typical Application Circuit                                                          | 20 |

| 9.2. Shunt Resistor Selection                                                             | 20 |

| 9.3. PCB LAYOUT                                                                           | 21 |

| 10. PACKAGE INFORMATION                                                                   | 22 |

| 11. ORDERING INFORMATION                                                                  |    |

| 12. DOCUMENTATION SUPPORT                                                                 |    |

|                                                                                           | _  |

| 13. TAPE AND REEL INFORMATION                                                             | 23 |

| 14. REVISION HISTORY                                                                      | 24 |

# 1. Pin Configuration and Functions

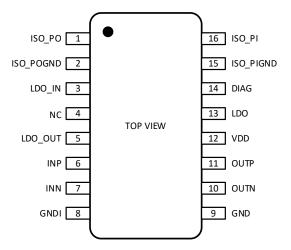

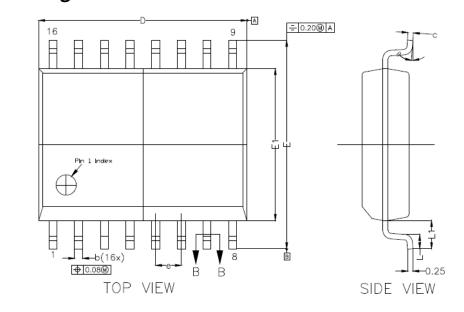

Figure 1.1 NSI3600D Package

Table 1.1 NSI3600D Pin Configuration and Description

| NSI3600D PIN NO. SYMBOL |           | FUNCTION                                                                                                              |

|-------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------|

| 1                       | ISO_PO    | Internal isolated power output (need to be connected to the LDO_IN pin)                                               |

| 2                       | ISO_POGND | Internal isolated power ground reference (need to be connected to the GNDI pin)                                       |

| 3                       | LDO_IN    | Internal input side LDO power input (need to be connected to the ISO_PO pin)                                          |

| 4                       | NC        | Not internal connected, leave this pin floating                                                                       |

| 5                       | LDO_OUT   | Internal input side LDO power output                                                                                  |

| 6                       | INP       | Positive analog input (Either INP or INN must have a DC current path to GNDI to define the common-mode input voltage) |

| 7                       | INN       | Negative analog input                                                                                                 |

| 8                       | GNDI      | Input side ground reference (need to be connected to the ISO_POGND pin)                                               |

| 9                       | GND       | Output side ground reference (need to be connected to the ISO_PIGND pin)                                              |

| 10                      | OUTN      | Negative analog output                                                                                                |

| 11                      | OUTP      | Positive analog output                                                                                                |

| 12                      | VDD       | Output side power supply                                                                                              |

| 13                      | LDO       | Internal output side LDO power output (need to be connected to the ISO_PI pin and without external load)              |

| 14                      | DIAG      | Open-drain diagnosis output (need to be connected to the pull-up supply or floating)                                  |

| 15                      | ISO_PIGND | Internal isolated power ground reference (need to be connected to the GND pin)                                        |

| 16                      | ISO_PI    | Internal isolated power input (need to be connected to the LDO pin)                                                   |

# 2. Absolute Maximum Ratings(1)

| Parameters               | Symbol           | Min     | Тур | Max         | Unit |

|--------------------------|------------------|---------|-----|-------------|------|

| Power Supply Voltage     | VDD to GND       | -0.3    |     | 6.5         | V    |

| Analog Input Voltage     | INP, INN         | GNDI-6  |     | LDO_OUT+0.5 | V    |

| Analog Output Voltage    | OUTP, OUTN       | GND-0.5 |     | VDD+0.5     | V    |

| Digital Output Voltage   | DIAG             | GND-0.5 |     | 6.5         | V    |

| Input current per IO Pin | I <sub>IN</sub>  | -10     |     | 10          | mA   |

| Junction Temperature     | TJ               | -40     |     | 150         | °C   |

| Storage Temperature      | T <sub>STG</sub> | -55     |     | 150         | °C   |

<sup>(1)</sup> The device cannot operate beyond the listed Absolute Maximum Ratings to prevent permanent device damage. The device is not fully functional if operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings. Long-time stress of the absolute maximum conditions may affect the device lifetime.

### 3. ESD Ratings

| Parameters              | Test Condition                                                                 | Value | Unit |

|-------------------------|--------------------------------------------------------------------------------|-------|------|

| Floatroctatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2.0  | kV   |

| Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1.0  | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 4. Recommended Operating Conditions

| Parameters                                        | Symbol                | Min   | Тур  | Max                  | Unit |

|---------------------------------------------------|-----------------------|-------|------|----------------------|------|

| Power Supply                                      | VDD toGNDI            | 3.0   | 3.3  | 5.5                  | V    |

| Differential input voltage before clipping output | V <sub>Clipping</sub> |       | ±320 |                      | mV   |

| Linear differential input full scale voltage      | $V_{FSR}$             | -250  |      | 250                  | mV   |

| Absolute common-mode input voltage                | V <sub>CM</sub>       | -2    |      | V <sub>LDO_OUT</sub> | V    |

| Operating common-mode input voltage               | $V_{CM}$              | -0.16 |      | 1                    | V    |

| DIAG pull-up supply voltage                       | $V_{DIAG}$            | 0     |      | VDD                  | V    |

| Operating Ambient Temperature                     | TA                    | -40   |      | 125                  | °C   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 5. Thermal Information

| Parameters                                   | Symbol              | SOP16(300mil) | Unit |

|----------------------------------------------|---------------------|---------------|------|

| Junction-to-ambient thermal resistance       | $R_{	heta JA}$      | 64            | °C/W |

| Junction-to-case (top) thermal resistance    | $R_{	heta JC(top)}$ | 30            | °C/W |

| Junction-to-board thermal resistance         | R <sub>θЈВ</sub>    | 33.3          | °C/W |

| Junction-to-top characterization parameter   | $\Psi_{JT}$         | 10.9          | °C/W |

| Junction-to-board characterization parameter | $\Psi_{JB}$         | 28.2          | °C/W |

# 6. Specifications

### **6.1. Electrical Characteristics**

$(VDD = 3.0V \sim 5.5V, INP = -250mV \text{ to } +250mV, \text{ and } INN = GNDI = 0V, T_A = -40^{\circ}C \text{ to } 125^{\circ}C.$  Unless otherwise noted, Typical values are at VDD = 3.3V,  $T_A = 25^{\circ}C$ )

| Parameters                                                           | Symbol                    | Min  | Тур  | Мах  | Unit  | Comments                                                                                                                                        |

|----------------------------------------------------------------------|---------------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supply                                                         |                           |      |      |      |       |                                                                                                                                                 |

| Output side supply voltage                                           | VDD                       | 3.0  | 3.3  | 5.5  | V     |                                                                                                                                                 |

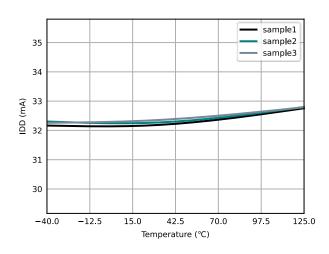

| Output side supply current                                           | IDD                       |      | 31.3 | 38.5 | mA    | No external load on LDO_OUT                                                                                                                     |

| Output side supply current                                           | IDD                       |      | 32.6 | 40   | mA    | 1mA external load on LDO_OUT                                                                                                                    |

| External load current on Input side LDO                              | I <sub>E</sub>            |      |      | 1    | mA    |                                                                                                                                                 |

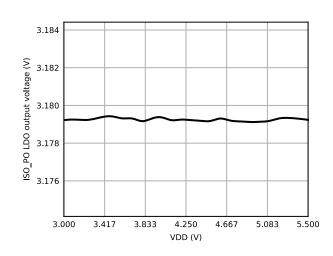

| Isolated power output voltage                                        | V <sub>ISO_PO</sub>       | 3.1  | 3.5  | 4.6  | V     | ISO_PO to GNDI                                                                                                                                  |

| Input side LDO output voltage                                        | V <sub>LDO_OUT</sub>      | 3    | 3.2  | 3.4  | V     | LDO_OUT to GNDI                                                                                                                                 |

| Isolated power output<br>undervoltage detection<br>threshold voltage | V <sub>ISO_POUV</sub>     | 2.1  | 2.3  | 2.8  | V     | Isolated power output falling                                                                                                                   |

| Input side LDO undervoltage detection threshold voltage              | $V_{\text{LDO}\_{	t UV}}$ | 2.1  | 2.3  | 2.8  | V     | LDO_OUT falling                                                                                                                                 |

| VDD undervoltage detection threshold voltage                         | VDD <sub>UV</sub>         |      |      | 2.95 | V     |                                                                                                                                                 |

| Analog Input                                                         |                           |      |      |      |       |                                                                                                                                                 |

| Input offset voltage                                                 | Vos                       | -0.2 | ±0.1 | 0.2  | mV    | INP = INN = GNDI, at T <sub>A</sub> = 25°C                                                                                                      |

| Input offset drift (1)                                               | TCVos                     | -3   | 1    | 3    | μV/°C |                                                                                                                                                 |

| Common-mode rejection ratio                                          | CMRR <sub>dc</sub>        |      | -100 |      | dB    | $INP = INN,  f_{IN} = 0  Hz,  V_{CM  min} \leq VIN \leq \\ V_{CM  max}$                                                                         |

| (2)                                                                  | $CMRR_{ac}$               |      | -98  |      | dB    | $\begin{split} & \text{INP = INN, } f_{\text{IN}} = 10 \text{ kHz, } V_{\text{CM min}} \leq \text{VIN} \\ & \leq V_{\text{CM max}} \end{split}$ |

| Parameters                           | Symbol                | Min    | Тур    | Мах   | Unit                 | Comments                                                                           |

|--------------------------------------|-----------------------|--------|--------|-------|----------------------|------------------------------------------------------------------------------------|

| Single-ended input resistance        | R <sub>IN</sub>       |        | 20     |       | kΩ                   | INN = GNDI                                                                         |

| Differential input resistance        | R <sub>IND</sub>      |        | 24     |       | kΩ                   |                                                                                    |

| Input capacitance                    | Cı                    |        | 4      |       | pF                   | Single-ended input capacitance, fin=310kHz                                         |

| Input capacitance                    | C <sub>ID</sub>       |        | 5      |       | pF                   | Differential input capacitance, fin=310kHz                                         |

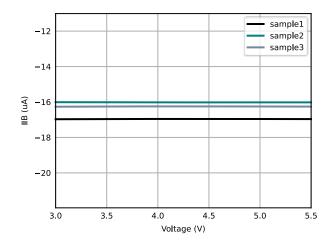

| Input bias current                   | I <sub>IB</sub>       | -20    | -16    | -13   | μА                   | $INP = INN = GNDI$ , $I_{IB} = (I_{IBP} + I_{IBN}) / 2$                            |

| Input bias current drift (1)         | TCI <sub>IB</sub>     |        | ±1     |       | nA/°C                |                                                                                    |

| Input offset current                 | I <sub>IO</sub>       |        | 10     |       | nA                   | I <sub>IO</sub> =  I <sub>IBP</sub> - I <sub>IBN</sub>                             |

| Analog Output                        |                       |        |        |       |                      |                                                                                    |

| Nominal Gain                         |                       |        | 8.2    |       | V/V                  |                                                                                    |

| Gain error                           | E <sub>G</sub>        | -0.3%  | ±0.05% | 0.3%  |                      | at T <sub>A</sub> =25°C                                                            |

| Gain error thermal drift (1)         | TCE <sub>G</sub>      | -50    | ±15    | 50    | ppm/°C               |                                                                                    |

| Nonlinearity                         |                       | -0.05% | ±0.01% | 0.05% |                      |                                                                                    |

| Nonlinearity drift (1)               |                       |        | 1      |       | ppm/°C               |                                                                                    |

| Total harmonic distortion (3)        | THD                   |        | -88    |       | dB                   | V <sub>IN</sub> =500mVpp, f <sub>IN</sub> = 10kHz, BW = 100kHz                     |

| Output noise                         |                       |        | 300    |       | $\mu V_{\text{RMS}}$ | INP = INN = GNDI, BW = 100kHz                                                      |

| Signal to pains votice               | SNR                   | 80     | 84     |       | dB                   | $V_{IN} = 500 \text{mVpp}, f_{IN} = 1 \text{kHz}, BW = 10 \text{kHz}$              |

| Signal to noise ratio                | SNR                   | 65     | 71     |       | dB                   | V <sub>IN</sub> = 500mVpp, f <sub>IN</sub> = 10kHz, BW = 100kHz, 1MHz filter       |

| Common-mode output voltage           | $V_{CMout}$           | 1.38   | 1.45   | 1.51  | V                    |                                                                                    |

| Differential clipping output voltage | $V_{CLout}$           |        | ±2.49  |       | V                    | $V_{OUT} = (V_{OUTP} - V_{OUTN}),$ $ V_{IN}  =  V_{INP} - V_{INN}  > V_{Clipping}$ |

| Failsafe differential output voltage | V <sub>FAILSAFE</sub> |        | -2.6   | -2.5  | V                    |                                                                                    |

| Output bandwidth                     | BW                    |        | 350    |       | kHz                  |                                                                                    |

|                                      | PSRR <sub>dc</sub>    |        | -109   |       | dB                   | PSRR vs VDD, from 3.0~5.5V at DC                                                   |

| Power supply rejection ratio (2)     | PSRR <sub>ac</sub>    |        | -98    |       | dB                   | PSRR vs VDD, 100mV and 10kHz ripple                                                |

| Output resistance                    | R <sub>оит</sub>      |        | 3      |       | Ω                    |                                                                                    |

| Output limit current                 | I <sub>lim</sub>      |        | ±20    |       | mA                   |                                                                                    |

| Common-mode transient immunity       | CMTI                  | 100    | 150    |       | kV/μs                | Common-mode transient immunity                                                     |

| Parameters                                      | Symbol          | Min | Тур | Max | Unit | Comments                                              |

|-------------------------------------------------|-----------------|-----|-----|-----|------|-------------------------------------------------------|

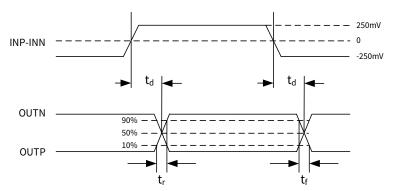

| Timing                                          |                 |     |     |     |      |                                                       |

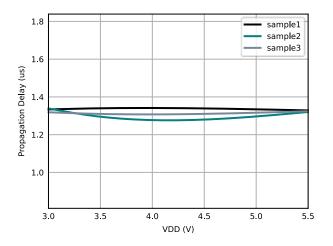

| Rising time of OUTP, OUTN                       | t <sub>r</sub>  |     | 1.3 |     | μs   |                                                       |

| Falling time of OUTP, OUTN                      | t <sub>f</sub>  |     | 1.3 |     | μs   |                                                       |

| INP, INN to OUTP, OUTN signal delay (50% - 50%) | t <sub>PD</sub> |     | 1.3 | 2   | μs   |                                                       |

| Analog setting time                             | <b>t</b> as     |     | 0.9 |     | ms   | VDD step to 3.0 V, to OUTP, OUTN valid, 0.1% settling |

- (1) The temperature drift is calculated within the whole temperature range (-40°C to 125°C).

- (2) Input referred.

- (3) THD is defined as the ratio of the sum of the rms value of first five higher harmonics to the amplitude of the fundamental (input referred).

#### 6.2. Timing Diagrams

Figure 6.1 Propagation Delay and Output Fall Time Definition

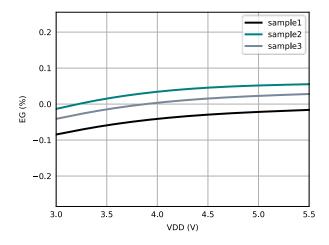

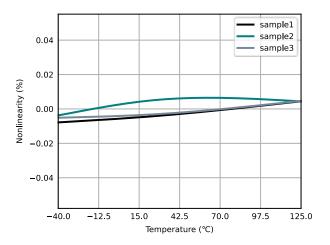

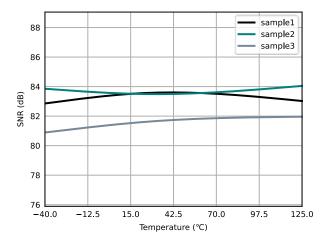

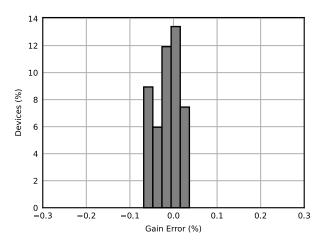

#### 6.3. Typical Performance Characteristics

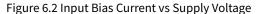

Figure 6.3 Input Bias Current vs Temperature

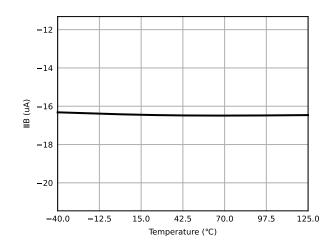

Figure 6.4 Input Bias Current vs Common-Mode Input Voltage

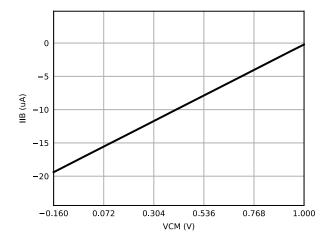

Figure 6.6 Input Offset Voltage vs Temperature

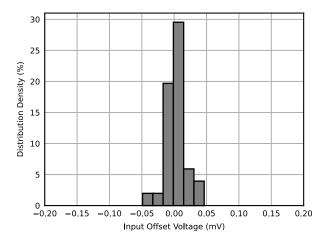

Figure 6.8 Input Offset Voltage Distribution(1)

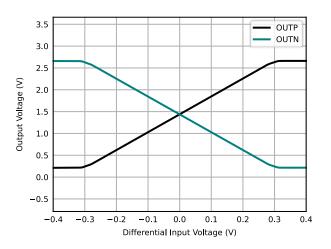

Figure 6.5 Output vs Differential Input Voltage

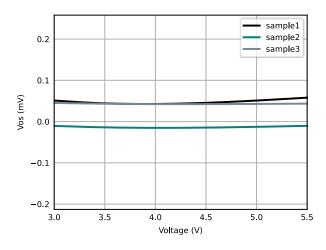

Figure 6.7 Input Offset Voltage vs Supply Voltage

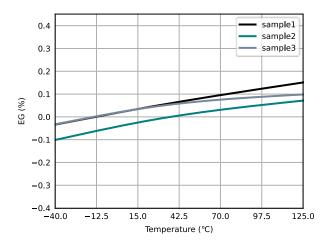

Figure 6.9 Gain Error vs Temperature

Figure 6.10 Gain Error vs Supply Voltage

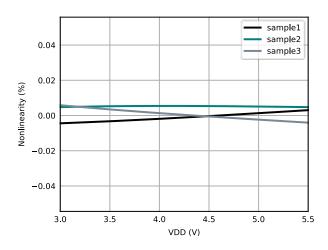

Figure 6.12 Nonlinearity vs Temperature

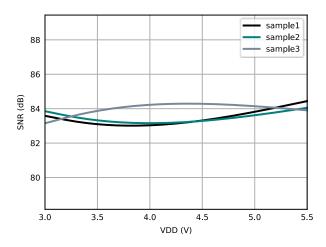

Figure 6.14 Signal to Noise Ratio vs Temperature

Figure 6.11 Gain Error Distribution<sup>(1)</sup>

Figure 6.13 Nonlinearity vs Supply Voltage

Figure 6.15 Signal to Noise Ratio vs Supply Voltage

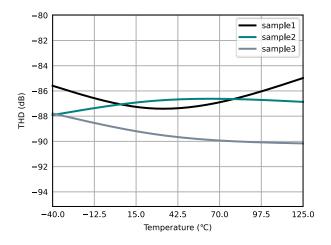

Figure 6.16 Total Harmonic Distortion vs Temperature

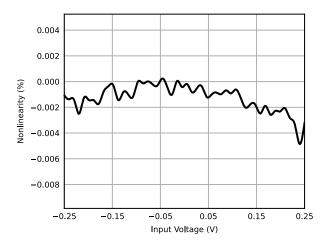

Figure 6.18 Nonlinearity vs Input Voltage

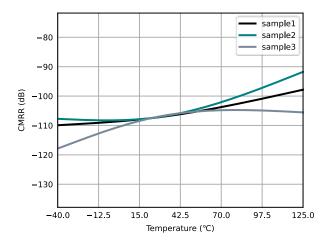

Figure 6.20 Common-Mode Rejection Ratio vs Temperature

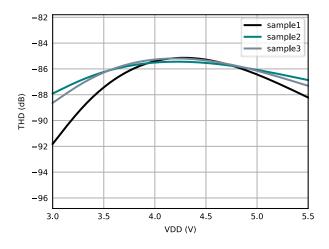

Figure 6.17 Total Harmonic Distortion vs Supply Voltage

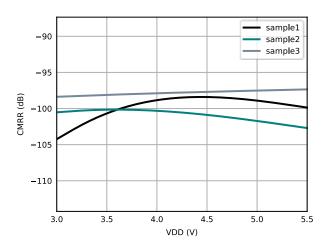

Figure 6.19 Common-Mode Rejection Ratio vs Supply Voltage

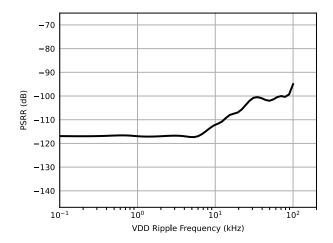

Figure 6.21 Power-Supply Rejection Ratio vs VDD Input Frequency

36 sample1 sample2 sample3

32 30 3.5 4.0 4.5 5.0 5.5 VDD (V)

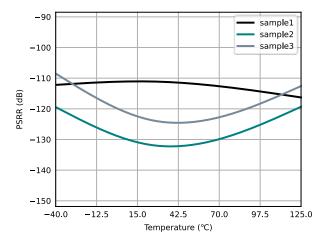

Figure 6.22 Power-Supply Rejection Ratio vs Temperature

Figure 6.23 Input Supply Current vs Supply Voltage (I<sub>E</sub>=1mA)

Figure 6.24 Input Supply Current vs Temperature (I<sub>E</sub>=1mA)

Figure 6.25 ISO-PO LDO Regulation

Figure 6.26 Input and Output Signal Delay time vs Supply Voltage

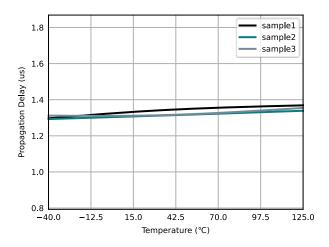

Figure 6.27 Input and Output Signal Delay time vs Temperature

(1) According to the test results of 30 pcs samples.

# 7. High Voltage Feature Description

# 7.1. Insulation and Safety Related Specifications

| Parameters                                          | Symbol | Value | Unit | Comments                                                                       |

|-----------------------------------------------------|--------|-------|------|--------------------------------------------------------------------------------|

| Minimum External Clearance                          | CLR    | 8     | mm   | IEC 60664-1:2007                                                               |

| Minimum External Creepage                           | CPG    | 8     | mm   | IEC 60664-1:2007                                                               |

| Distance Through Inculation                         | DTI    |       | μm   | Distance through insulation (internal clearance – capacitive signal isolation) |

| Distance Through Insulation                         | DTI    | 75    | μm   | Distance through insulation (internal clearance – transformer power isolation) |

| Tracking Resistance<br>(Comparative Tracking Index) | СТІ    | >600  | V    | DIN EN 60112 (VDE 0303-11); IEC 60112                                          |

| Material Group                                      |        | I     |      | IEC 60664-1                                                                    |

| Description                            | Test Condition                     | Value     |

|----------------------------------------|------------------------------------|-----------|

|                                        | For Rated Mains Voltage ≤ 150Vrms  | I to IV   |

| Overwellte as Catagorius au IECCOCCA 1 | For Rated Mains Voltage ≤ 300Vrms  | I to IV   |

| Overvoltage Category per IEC60664-1    | For Rated Mains Voltage ≤ 600Vrms  | I to IV   |

|                                        | For Rated Mains Voltage ≤ 1000Vrms | l to III  |

| Climatic Classification                |                                    | 40/125/21 |

| Pollution Degree per DIN VDE 0110      |                                    | 2         |

### 7.2. Insulation Characteristics

| Description                          | Test Condition                                                                                                                                                                  | Symbol            | Value | Unit              |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------------------|

| DIN EN IEC 60747-17 (VDE 0884-17)    |                                                                                                                                                                                 |                   |       |                   |

| Maximum repetitive isolation voltage |                                                                                                                                                                                 | V <sub>IORM</sub> | 2121  | V <sub>PEAK</sub> |

| Maximum working isolation voltage    | AC Voltage                                                                                                                                                                      | V <sub>IOWM</sub> | 1500  | $V_{RMS}$         |

| Maximum working isolation voltage    | DC Voltage                                                                                                                                                                      | VIOWM             | 2121  | V <sub>DC</sub>   |

|                                      | Method a, after Input/output safety test subgroup 2/3,                                                                                                                          |                   |       | pC                |

|                                      | $V_{\text{ini}}=V_{\text{IOTM}}$ , $t_{\text{ini}}=60 \text{ s}$ , $V_{\text{pd(m)}}=1.2*V_{\text{IORM}}$ , $t_{\text{m}}=10 \text{ s}$ .                                       |                   |       |                   |

| Apparent Charge                      | Method a, after environmental tests subgroup 1,<br>V <sub>ini</sub> =V <sub>IOTM</sub> , t <sub>ini</sub> =60s ,V <sub>pd(m)</sub> =1.6*V <sub>IORM</sub> , t <sub>m</sub> =10s | $q_{pd}$          | <5    | рС                |

|                                      | Method b, V <sub>ini</sub> =1.2*V <sub>IOTM</sub> , t <sub>ini</sub> =1s                                                                                                        |                   |       |                   |

|                                      | $V_{pd (m)}$ =1.875* $V_{IORM}$ , $t_m$ =1s (method b1) or $V_{pd (m)}$ = $V_{ini}$ , $t_m$ = $t_{ini}$ (method b2)                                                             |                   |       | pC                |

| Description                             | Test Condition                                                                              | Symbol            | Value             | Unit              |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|--|

| Maximum transient isolation voltage     | t = 60sec                                                                                   | V <sub>ІОТМ</sub> | 8000              | V <sub>PEAK</sub> |  |

| Maximum impulse voltage                 | Tested in air, 1.2/50μs waveform per IEC62368-1                                             | $V_{IMP}$         | 6250              | $V_{PEAK}$        |  |

| Maximum Surge Isolation Voltage         | Test method per IEC62368-1, 1.2/50μs waveform,<br>V <sub>IOSM</sub> ≥V <sub>IMP</sub> × 1.3 | V <sub>IOSM</sub> | 10000             | V <sub>PEAK</sub> |  |

|                                         | V <sub>IO</sub> =500V, T <sub>amb</sub> =25°C                                               | Rio               | >1012             | Ω                 |  |

| Isolation resistance                    | $V_{10} = 500V, 100^{\circ}C \le T_{amb} \le 125^{\circ}C$                                  | Rıo               | >10 <sup>11</sup> | Ω                 |  |

|                                         | $V_{10}$ =500V, $T_{amb}$ = $T_s$                                                           | R <sub>IO</sub>   | >109              | Ω                 |  |

| Isolation capacitance                   | f = 1MHz                                                                                    | Cıo               | 0.8               | pF                |  |

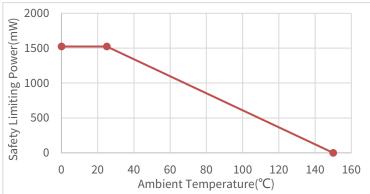

| Safety total power dissipation          | $V_1 = 5.5V$ , $T_J = 150$ °C, $T_A = 25$ °C                                                | Ps                | 1524              | mW                |  |

| Safety input, output, or supply current | $\theta_{JA}$ = 82°C/W for SOW8, $V_{I}$ = 5.5V, $T_{J}$ = 150 °C, $T_{A}$ = 25 °C          | Is                | 277               | mA                |  |

| Maximum safety temperature              |                                                                                             | Ts                | 150               | °C                |  |

| UL1577                                  |                                                                                             |                   |                   |                   |  |

| Insulation voltage per UL               | $V_{TEST} = V_{ISO}$ , $t = 60$ s (qualification), $V_{ISO}$                                |                   | 5000              | $V_{RMS}$         |  |

Figure 7.1 NSI3600D Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN VDE V 0884-11

#### 7.3. Regulatory Information

The NSI3600D are approved or pending approval by the organizations listed in table.

| U                                                            | L                                                            | VDE                                                                                                                                                 | coc                                | TUV                                      |

|--------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------|

| UL 1577 Component<br>Recognition Program                     | Approved under CSA<br>Component Acceptance<br>Notice 5A      | DIN EN IEC 60747-17<br>(VDE 0884-17)                                                                                                                | Certified according<br>to GB4943.1 | Certified According<br>to EN IEC 62368-1 |

| Single Protection, 5000V <sub>rms</sub><br>Isolation voltage | Single Protection,<br>5000V <sub>rms</sub> Isolation voltage | Reinforce Insulation V <sub>IORM</sub> =2121 V <sub>PEAK</sub> V <sub>IOTM</sub> =8000 V <sub>PEAK</sub> V <sub>IOSM</sub> =10000 V <sub>PEAK</sub> | Reinforced<br>insulation           | 5000Vrms for 1min                        |

| E500602                                                      | E500602                                                      | File (pending)                                                                                                                                      | CQC20001264939                     | R50574061                                |

### 8. Function Description

#### 8.1. Overview

The NSI3600D is a high performance isolated amplifier with integrated isolated power supply that accept fully-differential input. The fully-differential input is ideally suited for shunt current monitoring in high voltage applications where isolation is required.

The low-side power supply VDD feeds power to the isolated power supply input through an LDO with external connection from the LDO pin to the ISO\_PI pin. The output of the isolated power supply is regulated by an internal LDO with external connection from the ISO\_PO pin to the LDO\_IN pin, to power the high-side circuit. The integrated isolated power supply enables single-power operation on the low side of the device without the need for a separate isolated power supply for the high side, effectively reducing the board area.

The analog input is continuously sampled by a second-order  $\Sigma$ - $\Delta$  modulator in the device, which is driven by a pre-stage fully-differential amplifier in the device. With the internal voltage reference and clock generator, the modulator converts the analog input signal to a digital bitstream. The output of the modulator is transferred by the drivers (called TX in the Functional Block Diagram) across the isolation barrier that separates the isolated input and output side voltage. The received bitstream and clock are synchronized and processed, as shown in the Functional Block Diagram, by a fourth-order analog filter on the output side and has a differential output.

Figure 8.1 Function Block Diagram of NSI3600D

#### 8.2. Analog Input and output

There are two restrictions on the analog input signals (VINP and VINN).

- If the input voltage exceeds the range GND 6 V to VDD+ 0.5 V, the input current must be limited to 10 mA because the device input electrostatic discharge (ESD) diodes turn on.

- The linearity and noise performance of the device are ensured only when the analog input voltage remains within the specified linear full-scale range (FSR) and within the specified common-mode input voltage range.

For linear input range, the analog output of NSI3600D has a fixed gain of 8.2. If an input signal exceeding the clipping input range is applied to the NSI3600D ( $V_{IN} \ge V_{Clipping}$ ), the analog output will be clipped (typically, 2.49V for positive clipping and -2.49V for negative clipping).

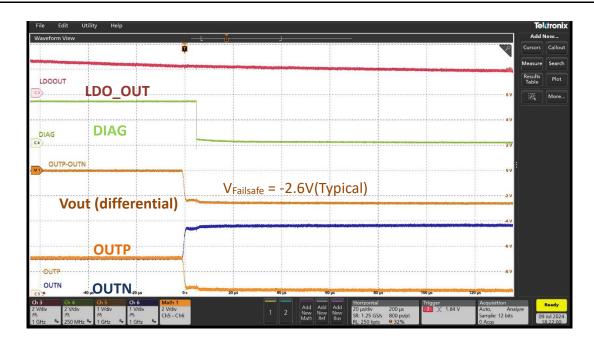

In addition, NSI3600D integrates some diagnostic measures and offers a fail-safe output to simplify system-level design. The fail-safe output is a negative differential output voltage that does not occur under normal device operation, and it will only be activated when the undervoltage of the integrated isolated power supply output ISO\_PO or the high-side LDO output LDO\_OUT is detected. Use the maximum V<sub>FAILSAFE</sub> voltage -2.5V as a reference value for the fail-safe detection on the system level.

#### 8.3. Accuracy Related Parameters

Parameters related to the accuracy performance are explained in this section, including Vos and its drift, EG and its drift, Nonlinearity. Other immunity parameters that affect accuracy like CMRR and PSRR are also included.

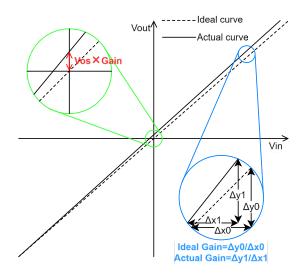

#### 8.3.1. Input offset Vos and Gain Error EG

Vos and EG are the most significant factor influencing accuracy. The ideal curve and actual curve are shown in Figure 8.2.

Figure 8.2 Vos and EG diagram

Vos means the input offset voltage when input is 0V. The tested output should be divided by nominal gain as Vos is defined as the offset voltage referred to input (See Equation 1).

Equation 1

where

- Vo is the output voltage tested when input is 0V.

- Nominal Gain is 8.2 for NSI3600D.

Gain is the magnification of the amplifier, and the definition formula is shown in Equation 2. EG means the difference between actual and ideal slope. It should be noted that EG is tested across the whole input range to minimize test error (See Equation 3).

$$Gain = \frac{\Delta y1}{\Delta x1} = \frac{Vo1 - Vo2}{Vin1 - Vin2}$$

Equation 2

$$E_G = \frac{Gain - Nominal \, Gain}{Nominal \, Gain} \times 100\%$$

Equation 3

where Vin1 and Vin2 are the lower and upper limit of the input FSR separately, Vo1 and Vo2 are the output voltage corresponding to Vin1 and Vin2.

#### 8.3.2. Input offset drift TCV<sub>os</sub> and Gain error thermal drift TCE<sub>G</sub>

Input offset drift TCVos means the drift of Vos over the whole operating temperature range, which is calculated as Equation 4.

$$TCVos = \frac{Vos_{max} - Vos_{min}}{TempRange}$$

Equation 4

where

- Vos<sub>max</sub> and Vos<sub>min</sub> is the maximum and minimum offset voltage over the whole operating ambient temperature range.

- TempRange covers the whole operating temperature, from -40°C to 125°C.

$Gain\ error\ thermal\ drift\ TCE_G\ is\ the\ drift\ of\ E_G\ over\ the\ whole\ operating\ temperature\ range,\ which\ is\ calculated\ as\ Equation\ 5.$

$$TCE_{G} = \frac{E_{Gmax} - E_{Gmin}}{TempRange}$$

Equation 5

where E<sub>Gmax</sub> and E<sub>Gmin</sub> is the maximum and minimum Gain Error over the whole temperature.

Both TCV<sub>OS</sub> and TCE<sub>G</sub> should be multiplied by the direction of temperature drift.

#### 8.3.3. Nonlinearity

Nonlinearity describes the deviation between the actual output and the ideal linear output. Calculate the peak-to-peak value of the error between the actual output and the fitting curve, and nonlinearity is expressed as the ratio of half of the peak-to-peak error to the full-scale range of the output voltage (See Equation 6).

Nonlinearity =

$$\frac{\text{Error\_pkpk}}{2 \times V_{\text{OFSR}}} \times 100\%$$

Equation 6

where

- Error\_pkpk is the peak-to-peak value of the error between the actual output and the fitting curve.

- V<sub>OFSR</sub> represents the full-scale range of the output voltage (4.1V for NSI3600D).

#### 8.3.4. Power-Supply Rejection Ratio

Power-Supply Rejection Ratio (PSRR) describes the level of the output error (input inferred) which is affected by the variation of power supply. PSRR is defined in dB and calculated as Equation 7.

$$PSRR = 20 \times log_{10} \left( \frac{V_{0\_var}}{Nominal \ Gain \times VDD_{var}} \right)$$

Equation 7

Where V<sub>O\_var</sub> and VDD<sub>var</sub> are respectively the variation value of the output voltage and the supply voltage.

#### 8.3.5. Common-Mode Rejection Ratio

Common-Mode Rejection Ratio (CMRR) quantifies the ability of a differential amplifier to suppress the variation of the common mode signals while amplifying the differential-mode signals. CMRR is calculated as:

$$CMRR = 20 \times \log_{10} \left( \frac{V_{0\_var}}{Nominal Gain \times V_{CM\_var}} \right)$$

Equation 8

where CMRR is the input-referred voltage variation in dB and V<sub>CM\_var</sub> is the variation value of the input common-mode voltage.

#### 8.3.6. Total Error Calculation

The total error is contributed by parameters discussed above. It is helpful to know the respective contribution of all different parameters when something is wrong about system current sensing. This section will introduce the calculation method of total error.

Parameters which mainly affects sensing accuracy are Vos, EG and Nonlinearity and their drift. PSRR and CMRR are not a dominant factor in most case. However, PSRR can be a concern when the power supply has high-frequency ripple, in which case a larger decoupling capacitor and a better layout is highly recommended (Refer to Section 9.3).

The error introduce by Vos and its drift can be calculated as:

$$Error\_Vos = \frac{Vos_{max} + TCV_{os} \times \Delta T}{V_{IN}} \times 100\%$$

Equation 9

where

- Vos<sub>max</sub> is the maximum value of input offset voltage at 25°C, which is ±0.2mV for NSI3600D.

- TCV<sub>os</sub> is the maximum drift of input offset voltage over the whole working temperature, which is 3uV/°C for 3600D

- ΔT is the range of temperature variation.

- V<sub>IN</sub> is the input voltage in the application.

The error introduced by E<sub>G</sub> and TCE<sub>G</sub> can be calculated as:

$$Error_E_G = E_G + TCE_G \times \Delta T$$

Equation 10

where

- E<sub>G</sub> is the maximum value of Gain Error when the temperature is 25°C, which is ±0.3% for NSI3600D.

- TCE<sub>G</sub> is the maximum drift of Gain Error over the whole temperature, which is ±50ppm/°C for NSI3600D.

The error introduced by Nonlinearity is Nonlinearity<sub>max</sub>, the maximum value of Nonlinearity in the entire temperature range, - 40°C to 125°C, which is ±0.05% for NSI3600D. The total error sensing error is expressed as:

Total\_Error =

$$\sqrt{\text{Error_Vos}^2 + \text{Error_E}_G^2 + \text{Nonlinearity}_{\text{max}}^2}$$

Equation 11

For example, consider an NSI3600D with the sensing input voltage of ±250mV and a - 40°C to 85°C temperature range. The total error calculation is shown in Table 1.

| Table 8.1 Total Error Calculation of NSI3600D (- 40°C to 85°C) |                             |                                                                                                                                                                                               |         |                       |  |  |  |

|----------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|--|--|--|

| Error<br>Component                                             | Symbol                      | Symbol Equation                                                                                                                                                                               |         | Error at<br>Vin=±25mV |  |  |  |

| Input offset<br>error                                          | Error_Vos                   | $Error_Vos = \frac{Vos_{max} + TCV_{os} \times \Delta T}{V_{IN}} \times 100\%$ $= \frac{\frac{\pm 0.2 \text{mV} \pm 3\mu \text{V/}^{\circ}\text{C}*65^{\circ}\text{C}}}{V_{IN}} \times 100\%$ | ±0.158% | ±1.58%                |  |  |  |

| Gain error                                                     | Error_E <sub>G</sub>        | Error_ $E_G = E_G + TCE_G \times \Delta T$<br>= $\pm 0.3\% \pm 50$ ppm/°C × 65°C                                                                                                              | ±0.625% | ±0.625%               |  |  |  |

| Nonlinearity                                                   | Nonlinearity <sub>max</sub> | Nonlinearity <sub>max</sub> = $\pm 0.05\%$                                                                                                                                                    | ±0.05%  | ±0.05%                |  |  |  |

| Total error                                                    | Total_Error                 | Total_Error $= \sqrt{\text{Error_Vos}^2 + \text{Error_E}_G^2 + \text{Nonlinearity}_{\text{max}}^2}$                                                                                           | ±0.647% | ±1.70%                |  |  |  |

Since the input offset voltage is independent of input voltage, it becomes the dominant factor of the total error when the input voltage is low. To improve the system accuracy, especially under low-input applications, it is recommended to perform software zero-point calibration and gain error calibration. With system-level calibration, the total error can also be reduced significantly. The reduced error is calculated as Table 8.2.

| Error<br>Component    | Symbol                      | Equation                                                                                                                                                                   | Error at<br>Vin=±250mV | Error at<br>Vin=±25mV |

|-----------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|

| Input offset<br>error | Error_Vos                   | Error_Vos = $\frac{\text{TCV}_{\text{os}} \times \Delta \text{T}}{\text{V}_{IN}} \times 100\%$ $= \frac{3\mu\text{V}/\text{°C} * 65\text{°C}}{\text{V}_{IN}} \times 100\%$ | ±0.078%                | ±0.78%                |

| Gain error            | Error_E <sub>G</sub>        | $Error_E_G = TCE_G \times \Delta T = \pm 50 \text{ppm/}^{\circ}C \times 65^{\circ}C$                                                                                       | ±0.325%                | ±0.325%               |

| Nonlinearity          | Nonlinearity <sub>max</sub> | Nonlinearity <sub>max</sub> = $\pm 0.05\%$                                                                                                                                 | ±0.05%                 | ±0.05%                |

| Total error           | Error_NSI1311               | Total_Error $= \sqrt{\text{Error_Vos}^2 + \text{Error_E}_G^2 + \text{Nonlinearity}_{\text{max}}^2}$                                                                        | ±0.338%                | ±0.846%               |

Table 8.2 Total Error Calculation with Software Calibration (- 40°C to 85°C)

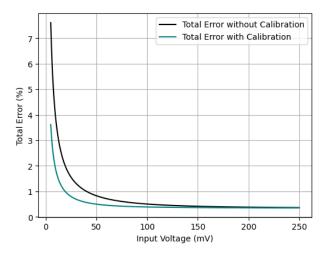

The maximum total error with and without calibration is show in Figure 8.3, considering 250mV input as full load, NSI3600D can achieve <1% error at more than 10% load(Vin≥25mV) with software calibration, and <1% error at more than 20% load(Vin≥50mV) without software calibration.

Figure 8.3 Total Error Over - 40°C to 85°C vs Input Voltage

#### 8.4. Isolated power

The NSI3600D integrates an isolated DC/DC power supply that includes the following components as shown in Figure 8.1:

- Low-side low-dropout regulator (LDO) to provide stable voltage for the input of the isolated DC/DC converter.

- Isolated DC/DC converter with the primary resonator and driver, an air-core transformer, and the secondary rectifier. The converter does not output a constant voltage and it is not recommended to drive additional load.

- High-side LDO to convert the isolated DC/DC converter output to a stable voltage and supply for the high-side signal circuitry. The high-side LDO can provide a limited current of 1mA for external load.

The isolated DC/DC power supply uses a spread spectrum clocking technique and optimized transformer design to improve the electro-magnetic interference (EMI) performance.

#### 8.5. Diagnostic Output

The open-drain diagnosis output DIAG helps confirm whether the device is in normal operation and simplifies system-level design and diagnostics. The DIAG pin needs to be connected to the pull-up supply through a resister. If the device operates normally, the DIAG pin is in a high-impedance state and pulled up to high level externally. The DIAG pin is actively pulled low when the undervoltage of the integrated isolated power supply output ISO\_PO or the high-side LDO output LDO\_OUT is detected. The failsafe mode is activated correspondingly. The amplifier outputs a negative differential voltage VFAILSAFE. During power-up, the DIAG pin is actively pulled low until the isolated power supply output voltage is established and the amplifier output voltage is valid.

The DIAG pin can be floating if not used.

Figure 8.4 Typical Failsafe output

### 9. Application Note

#### 9.1. Typical Application Circuit

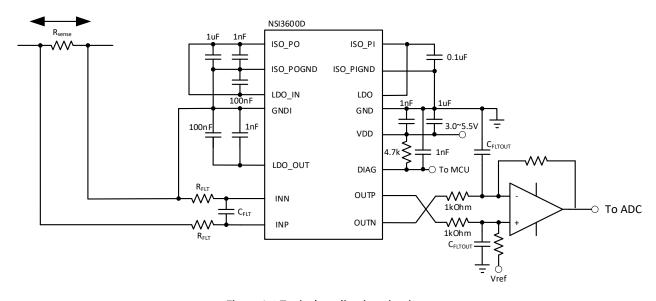

The following key features make NSI3600D the ideal solution for high accuracy isolated current measurement.

- Reinforced isolation barrier supports a working voltage up to 1500Vrms, provide extremely high reliability for dangerous high voltage systems.

- Excellent common mode transient immunity(CMTI, 150kV/us typ) ensures the device to provide accurate and reliable measurements even in the presence of high-power switching.

- Isolated power supply integrated, reduces the need of external isolated high-side supply compared to traditional <u>NSI1300D25</u>, simplifies design and reduces area.

- Excellent DC accuracy and low drift, high linearity over FSR, limited sensitivity to external magnetic fields, make sure the device can provide extremely high sensing accuracy.

Figure 9.1 shows the typical application circuit of NSI3600D. The output of the low-side LDO (LDO pin) need to be connected to the isolated power supply input (ISO\_PI pin). The isolated power supply output (ISO\_PO pin) need to be connected to the input of the high-side LDO (LDO\_IN pin). In this way, the high-side amplifier circuitry is powered by an isolated power supply. The necessary filter and bypass capacitors should be added to the device power supply pins, the output side power supply(VDD pin), the isolated power supply input (ISO\_PI pin) and output (ISO\_PO pin), and the input/output of the high-side LDO (LDO\_IN and LDO\_OUT pin). The recommended capacitance can refer to Figure 9.1.

The voltage across the shunt resistor  $R_{\text{sense}}$  is applied to the differential input of the NSI3600D through a RC filter. The differential output of the isolated amplifier is converted to a single-ended analog output with an operational-amplifier-based circuit. Suggest to add >1k $\Omega$  resistor on the OUTP and OUTN pin to prevent output over-current. An analog-to-digital converter usually receives the analog output and converts to digital signal for controller processing.

Figure 9.1 Typical application circuit

#### 9.2. Shunt Resistor Selection

Choosing a particular shunt resistor is usually a compromise between minimizing power dissipation and maximizing accuracy. Smaller sense resistor decreases power dissipation, while larger sense resistor can improve measure accuracy by utilizing the full input range of isolated amplifier.

There are two other factors should be considered when selecting the shunt resistor:

• The voltage-drop caused by the rated current range must not exceed the recommended linear input voltage range: V<sub>SHUNT</sub> ≤ FSR.

• The voltage-drop caused by the maximum allowed overcurrent must not exceed the input voltage that causes a clipping output: V<sub>SHUNT</sub> ≤ V<sub>Clipping</sub>.

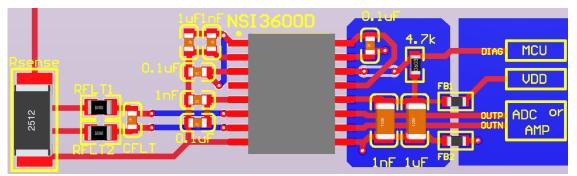

#### 9.3. PCB Layout

There are some key guidelines or considerations for optimizing performance in PCB layout:

- The filter and bypass capacitors of VDD, ISO\_PO, ISO\_PI and LDO\_OUT pins should be placed as close as possible to the pins respectively. For multiple filter capacitors of the same pin, capacitors with smaller values should be placed closer to the pin to filter out high-frequency noise better. An additional 1~10μF capacitor may be used for the power supply pin VDD in noisy conditions.

- Kelvin rules is recommended for the connection between shunt resistor to NSI3600D. Because of the Kelvin connection, any voltage drops across the trace and leads should have no impact on the measured voltage.

- Place the shunt resistor close to the INP and INN inputs and keep the layout of both connections symmetrical and run very

close to each other to the input of the NSI3600D. This minimizes the loop area of the connection and reduces the possibility

of stray magnetic fields from interfering with the measured signal.

- To suppress radiation on the power lines, place Ferrite Beads respectively in series with the line of VDD and GND for filter. The ferrite Beads, together with decoupling capacitors, can filter and isolate noise well. In the layout area, the ferrite beads need to effectively separate the chip layout area from peripheral circuit without overlap in different PCB layers. Ferrite Beads can also be added in series with the differential input to suppress radiation on the input signal lines.

- Keep the trace lengths of the wiring as short as possible and don't place a ground plane in the high-voltage domain, which minimizes the antenna on this node to minimize radiated emissions.

Figure 9.2 PCB layout example of NSI3600D

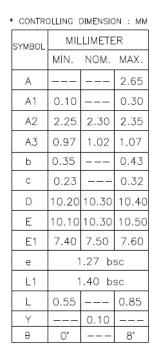

# 10. Package Information

NOTES

1.0 COPLANARITY APPLIES TO LEADS, CORNER LEADS AND DIE ATTACH PAD.

Figure 10.1 SOW16 package shape and dimension in millimeters

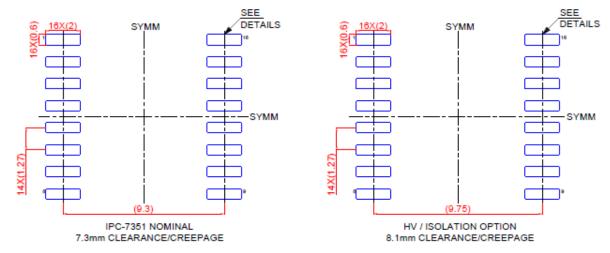

LAND PATTERN EXAMPLE(mm)

Figure 10.2 SOW16 Package Board Layout Example

# 11. Ordering Information

| Part No.          | Isolation<br>Rating(kV) | Linear Input<br>Range(mV) | Moisture<br>Sensitivity<br>Level | Temperature | Automotive | Package<br>Type   | Package<br>Drawing | SPQ  |

|-------------------|-------------------------|---------------------------|----------------------------------|-------------|------------|-------------------|--------------------|------|

| NSI3600D-<br>DSWR | 5                       | -0.25 ~ 0.25              | Level-2                          | -40 to 125℃ | NO         | SOP16<br>(300mil) | SOW16              | 1000 |

# 12. Documentation Support

| Part Number | Product Folder | Datasheet  | Technical Documents | Isolator selection guide |

|-------------|----------------|------------|---------------------|--------------------------|

| NSI3600D    | Click here     | Click here | Click here          | Click here               |

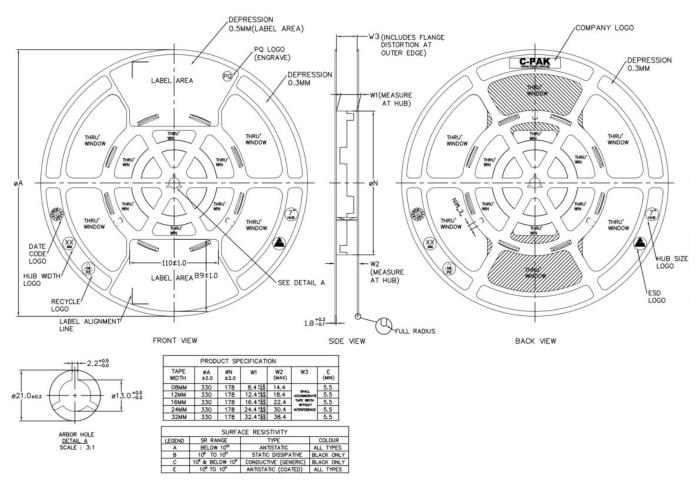

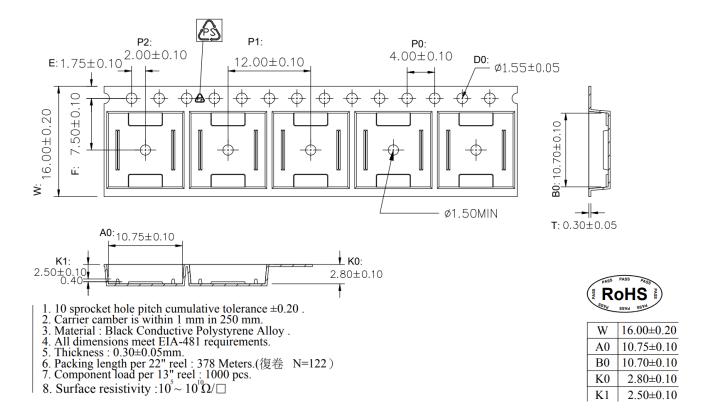

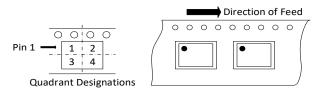

# 13. Tape and Reel Information

Figure 13.1 Tape Information

Figure 13.2 Reel Information of SOP16(300mil)

# 14. Revision History

| Revision | Description      | Date      |

|----------|------------------|-----------|

| 1.0      | Initial Version. | 2025/1/14 |

#### IMPORTANT NOTICE

The information given in this document (the "Document") shall in no event be regarded as any warranty or authorization of, express or implied, including but not limited to accuracy, completeness, merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

Users of this Document shall be solely responsible for the use of NOVOSENSE's products and applications, and for the safety thereof. Users shall comply with all laws, regulations and requirements related to NOVOSENSE's products and applications, although information or support related to any application may still be provided by NOVOSENSE.

This Document is provided on an "AS IS" basis, and is intended only for skilled developers designing with NOVOSENSE's products. NOVOSENSE reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided without notice. NOVOSENSE authorizes users to use this Document exclusively for the development of relevant applications or systems designed to integrate NOVOSENSE's products. No license to any intellectual property rights of NOVOSENSE is granted by implication or otherwise. Using this Document for any other purpose, or any unauthorized reproduction or display of this Document is strictly prohibited. In no event shall NOVOSENSE be liable for any claims, damages, costs, losses or liabilities arising out of or in connection with this Document or the use of this Document.

For further information on applications, products and technologies, please contact NOVOSENSE (www.novosns.com).

Suzhou NOVOSENSE Microelectronics Co., Ltd